# CS221: Logic Design

### Instructors: Dr. Ahmed Shalaby <u>http://bu.edu.eg/staff/ahmedshalaby14#</u> Dr. Fatma Sakr

#### **Digital Fundamentals**

#### CHAPTER Counters

#### Counters

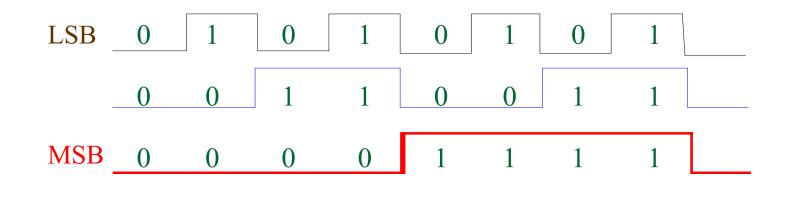

Counting in Binary

As you know, the binary count sequence follows a familiar pattern of 0's and 1's.

The next bit changes on every fourth number.

LSB changes on every number.

The next bit changes on every other number.

#### Counters

#### Counting in Binary

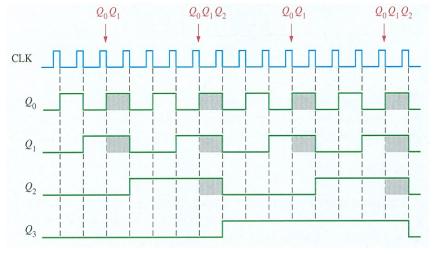

A counter can form the same pattern of 0's and 1's with logic levels. The first stage in the counter represents the least significant bit – notice that these waveforms follow the same pattern as counting in binary.

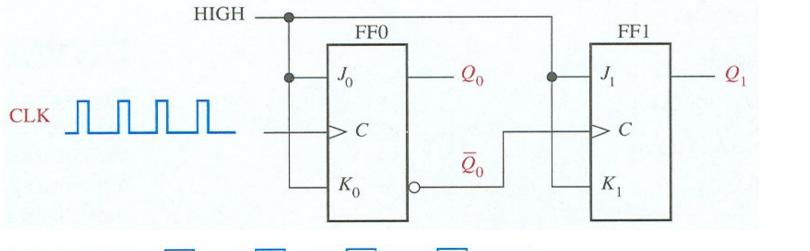

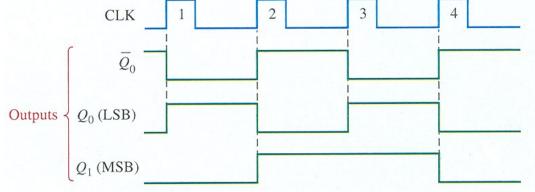

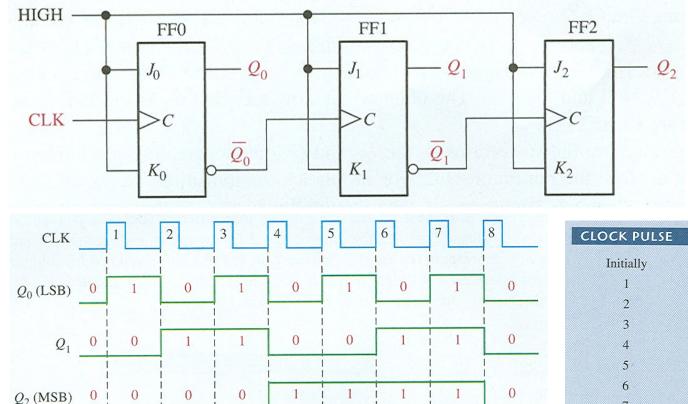

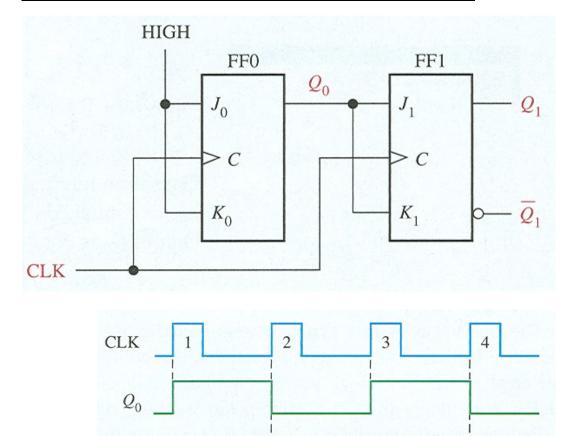

In an asynchronous counter, the clock is applied only to the first stage.

Subsequent stages derive the clock from the previous stage.

It uses J-K flip-flops in the toggle mode.

Notice that the Q0 output is triggered on the leading edge of the clock signal. The following stage is triggered from Q0.

#### 2-bit Asynchronous binary counter

| CLOCK PULSE  | <i>Q</i> <sub>1</sub> | $Q_0$ |  |

|--------------|-----------------------|-------|--|

| Initially    | 0                     | 0     |  |

| 1            | 0                     | 1     |  |

| 2            | 1                     | 0     |  |

| 3            | 1                     | 1     |  |

| 4 (recycles) | 0                     | 0     |  |

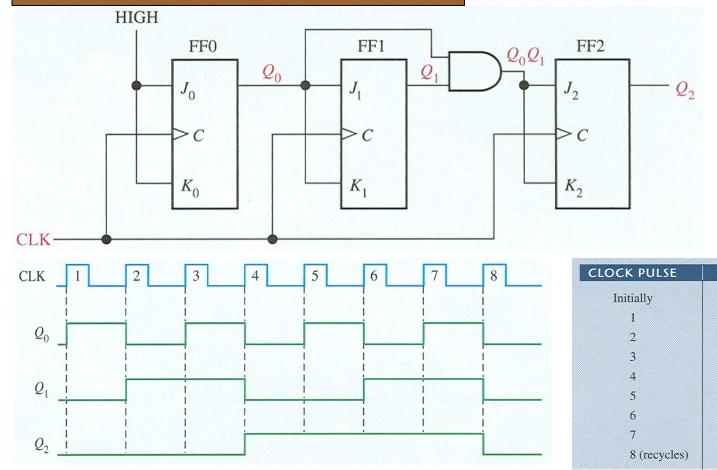

#### 3-bit Asynchronous binary counter

| 5            | 1 | 0 | 1 |

|--------------|---|---|---|

| 7            | 1 | 1 | 1 |

| 8 (recycles) | 0 | 0 | 0 |

$Q_2$

0

0

0

0

$Q_1$

0

0

1

1

$Q_0$

0

1

0

1

Copyright ©2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

Recycles back to 0

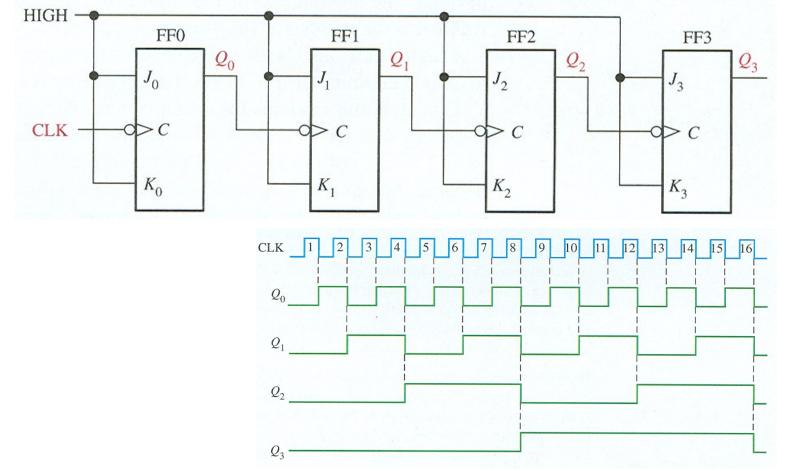

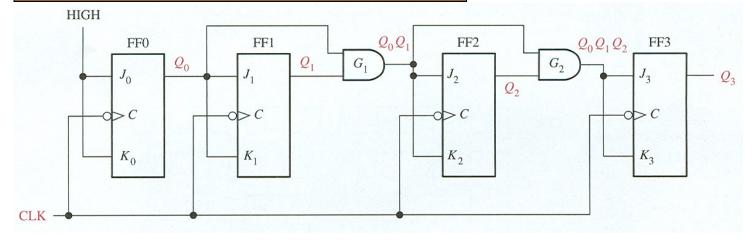

#### 4-bit Asynchronous binary counter

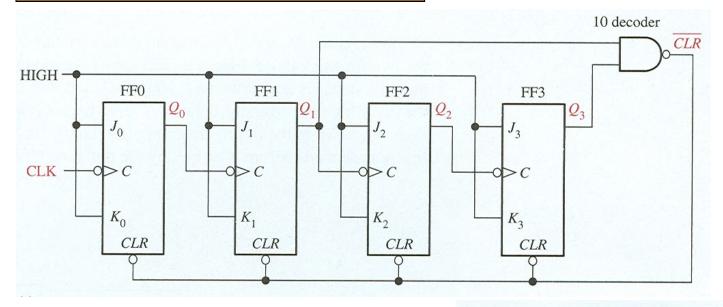

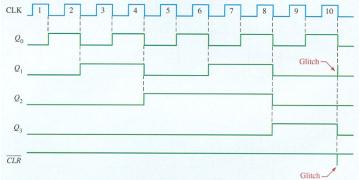

#### Asynchronous decade counter

#### Propagation Delay

Asynchronous counters are sometimes called **ripple** counters, because the stages do not all change together. For certain applications requiring high clock rates, this is a major disadvantage.

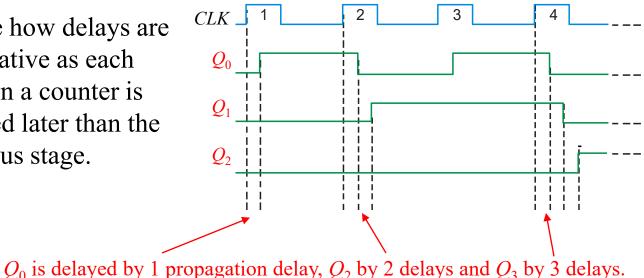

Notice how delays are cumulative as each stage in a counter is clocked later than the previous stage.

Synchronous Counters

In a synchronous counter all flip-flops are clocked together with a common clock pulse.

Synchronous counters overcome the disadvantage of accumulated propagation delays, but generally they require more circuitry to control states changes.

#### 2-bit Synchronous binary counter

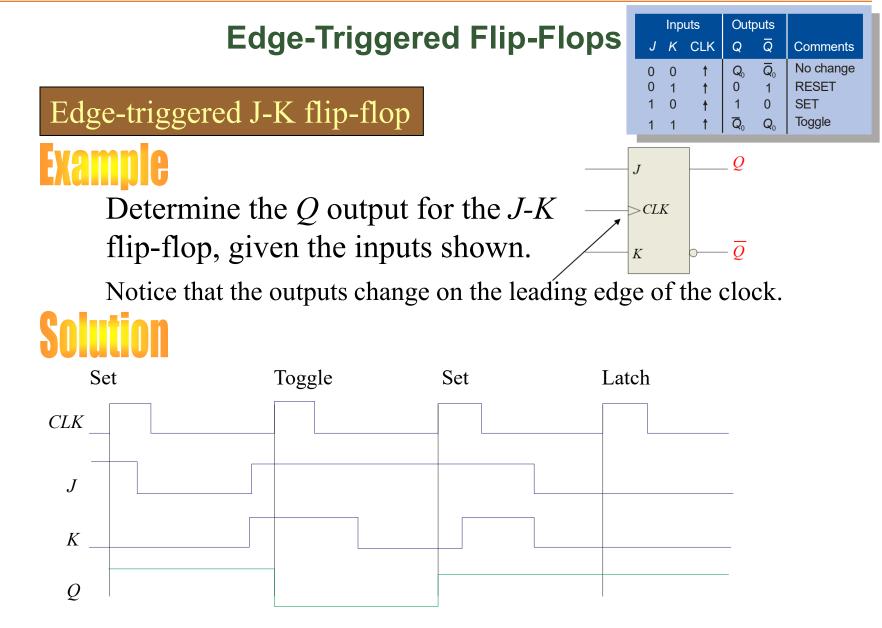

| I |   | Inp | uts | Outputs            |                    |           |

|---|---|-----|-----|--------------------|--------------------|-----------|

| I | J | Κ   | CLK | Q                  | Q                  | Comments  |

|   | 0 | 0   | 1   | $Q_0$              | $\overline{Q}_{0}$ | No change |

|   | 0 | 1   | 1   | 0                  | 1                  | RESET     |

|   | 1 | 0   | +   | 1                  | 0                  | SET       |

|   | 1 | 1   | 1   | $\overline{Q}_{0}$ | $Q_0$              | Toggle    |

Copyright ©2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

$Q_1$

#### 3-bit Synchronous binary counter

Copyright ©2006 by Pearson Education, Inc. Upper Saddle River, New Jersey 07458 All rights reserved.

$Q_2$

$Q_1$

$Q_0$

#### 4-bit Synchronous binary counter

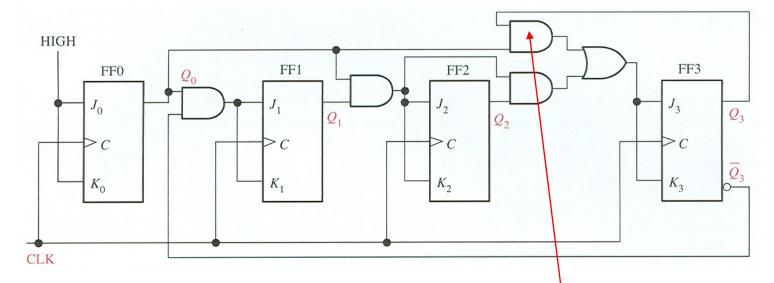

The 4-bit binary counter has one more AND gate than the 3-bit counter just described. The shaded areas show where the AND gate outputs are HIGH causing the next FF to toggle.

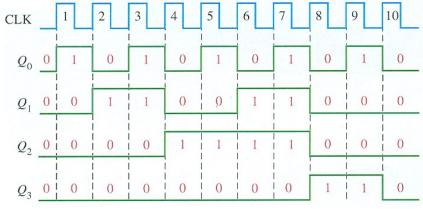

#### Synchronous decade counter

This gate detects 1001, and causes FF3 to toggle on the next clock pulse. FF0 toggles on every clock pulse. Thus, the count starts over at 0000.

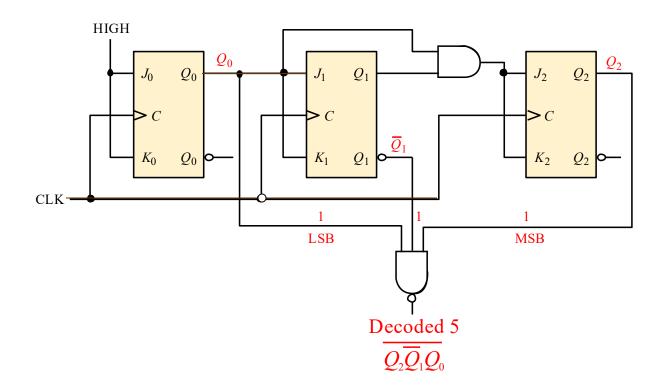

Counter Decoding

## Example

Show how to decode state 5 with an active LOW output.

#### A 4-bit Synchronous Binary Counter

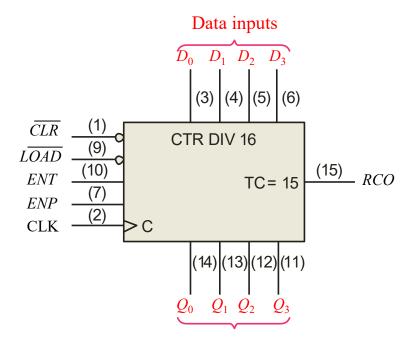

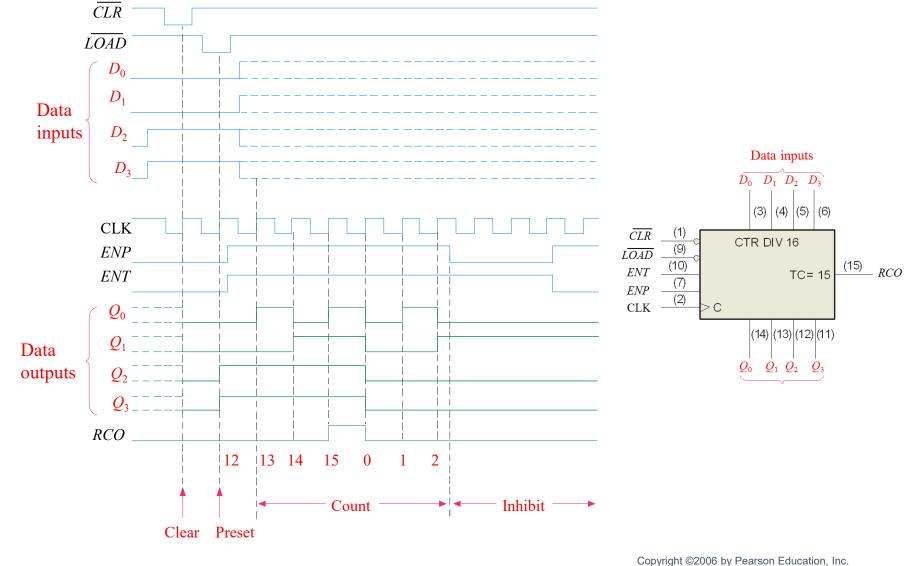

The 74LS163 is a 4-bit IC synchronous counter with additional features over a basic counter. It has parallel load, a  $\overline{CLR}$  input, two chip enables, and a ripple count output that signals when the count has reached the terminal count.

#### A 4-bit Synchronous Binary Counter

#### Cascaded counters

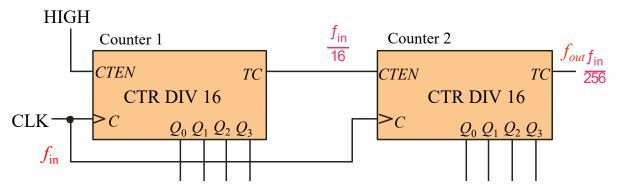

Cascading is a method of achieving higher-modulus counters. For synchronous IC counters, the next counter is enabled only when the terminal count of the previous stage is reached.

- a) What is the modulus of the cascaded DIV 16 counters?

b) If f<sub>in</sub> =100 kHz, what is f<sub>out</sub>?

- a) Each counter divides the frequency by 16. Thus the modulus is  $16^2 = 256$ .

- b) The output frequency is 100 kHz/256 = 391 Hz

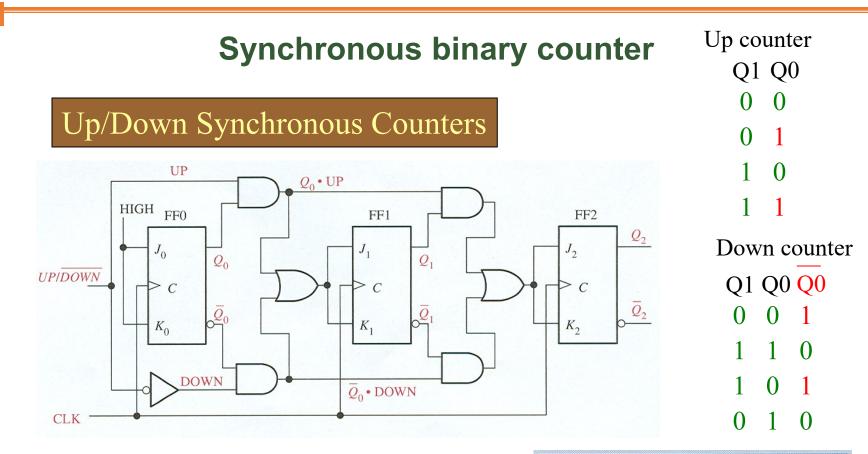

An up/down counter is capable of progressing in either direction depending on a control input.

| CLOCK PULSE | UP  | $Q_2$ | <b>Q</b> <sub>1</sub> | $Q_0$ | DOWN                      |

|-------------|-----|-------|-----------------------|-------|---------------------------|

| 0           | K   | 0     | 0                     | 0     | 51                        |

| 1           | 12  | 0     | 0                     | 1     | $\langle \langle \rangle$ |

| 2           | 1/2 | 0     | 1                     | 0     | $\langle \rangle$         |

| 3           |     | 0     | 1                     | 1     | 2                         |

| 4           |     | 1     | 0                     | 0     | 2                         |

| 5           | 15  | 1     | 0                     | 1     | 2                         |

| 6           | 115 | 1     | 1                     | 0     | 21                        |

| 7           | 16  | 1     | 1                     | 1     | )/                        |

#### Synchronous Counter Design

Most requirements for synchronous counters can be met with available ICs. In cases where a special sequence is needed, you can apply a step-by-step design process.

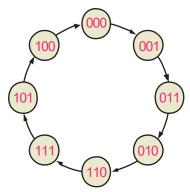

Start with the desired sequence and draw a state diagram and nextstate table. The gray code sequence from the text is illustrated:

State diagram:

#### Next state table:

| Present State  |                       |       | Next State     |                |                |

|----------------|-----------------------|-------|----------------|----------------|----------------|

| Q <sub>2</sub> | <b>Q</b> <sub>1</sub> | $Q_0$ | Q <sub>2</sub> | Q <sub>1</sub> | Q <sub>0</sub> |

| 0              | 0                     | 0     | 0              | 0              | 1              |

| 0              | 0                     | 1     | 0              | 1              | 1              |

| 0              | 1                     | 1     | 0              | 1              | 0              |

| 0              | 1                     | 0     | 1              | 1              | 0              |

| 1              | 1                     | 0     | 1              | 1              | 1              |

| 1              | 1                     | 1     | 1              | 0              | 1              |

| 1              | 0                     | 1     | 1              | 0              | 0              |

| 1              | 0                     | 0     | 0              | 0              | 0              |

#### Synchronous Counter Design

The J-K transition table lists all combinations of present output  $(Q_N)$  and next output  $(Q_{N+1})$  on the left. The inputs that produce that transition are listed on the right.

| Output                                                                                                                  | Flip-Flop                |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Transitions                                                                                                             | Inputs                   |

| Q <sub>N</sub> Q <sub>N+1</sub>                                                                                         | J K                      |

| $\begin{array}{c} 0 \longrightarrow 0 \\ 0 \longrightarrow 1 \\ 1 \longrightarrow 0 \\ 1 \longrightarrow 1 \end{array}$ | 0 X<br>1 X<br>X 1<br>X 0 |

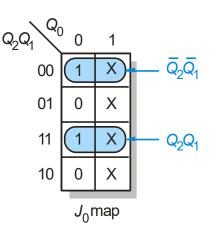

Each time a flip-flop is clocked, the *J* and *K* inputs required for that transition are mapped onto a K-map.

An example of the  $J_0$  map is:

| Pres           | sent S                | tate       | Ne                    | Next State            |                |  |

|----------------|-----------------------|------------|-----------------------|-----------------------|----------------|--|

| Q <sub>2</sub> | <b>Q</b> <sub>1</sub> | <b>Q</b> 0 | <b>Q</b> <sub>2</sub> | <b>Q</b> <sub>1</sub> | Q <sub>0</sub> |  |

| 0              | 0                     | 0          | 0                     | 0                     | 1              |  |

| 0              | 0                     | 1          | 0                     | 1                     | 1              |  |

| 0              | 1                     | 1          | 0                     | 1                     | 0              |  |

| 0              | 1                     | 0          | 1                     | 1                     | 0              |  |

| 1              | 1                     | 0          | 1                     | 1                     | 1              |  |

| 1              | 1                     | 1          | 1                     | 0                     | 1              |  |

| 1              | 0                     | 1          | 1                     | 0                     | 0              |  |

| 1              | 0                     | 0          | 0                     | 0                     | 0              |  |

|                |                       |            |                       |                       |                |  |

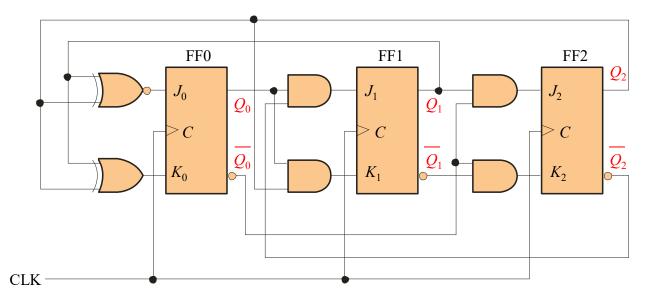

#### Synchronous Counter Design

The logic for each input is read and the circuit is constructed. The slide shows the circuit for the gray code counter...